| Mark-8 Design | Microcomputer According to Titus | Microcontroller Project | Postscriptum | Lessons Home |

Lesson 5: Pico CPU and Memory

The processor is a Parallax SX28AC/DP-G is run on RSIC architecture running up to 75 MHz. The SX-28 offers 4-stage instruction pipeline. The processor has 28 pins, 20 of which can be configured for I/O usage. The SX-28 processor has registers whose bits are directly connected to the board with I/O pins. Another important part of the XGS Pico is the oscillator; the SX-28 can accommodate an external oscillator and is capable of running up to 75 or 80 Mhz. The SX-28 contains 2K x 12 internal EE/Flash program memory which is used to store program code and is also accessible during program execution for storage purposes.

Contents [hide]

Registers

The data memory of the SX28 consists of a small number of byte-sized registers. Although there are well over 100 registers, only 32 are used to program the SX processor. The SX28 has the ability to bank registers which allows you to get all of the registers. For the XGS Pico there are 3 main I/O registers, RA, RB, and RC. The first half of the RA register (bytes 0 – 3) is used to control the LED’s on the Pico board. The RB register is used to control input from the user and the RC register is the output register. Another important register, the W register is the working register and is usually one of the operands in the instructions.

Architecture

The programs that run on the processor is a constant loop and will react as to what is in the registers, if an input is put into the processor it changes the program according to what the code specifies until it is no longer receiving that input. The XGS Pico does not run on a Von Newman Architecture, although it does have interrupts and interrupt handling. The entire architecture of the program is revolved around the code constantly looping and handling changes in the program directly instead of the Von Newman way which just sits and waits for an input to come change the state of the program. This is important to know because now it must be taken into consideration that a register might change at the wrong time meaning time management is very important for the XGS Pico.

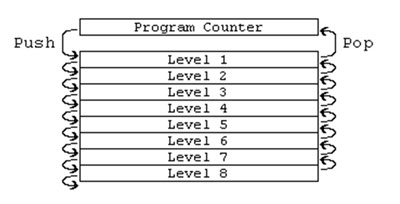

Stack

The stack is used to keep track of where the program execution should return when a subroutine completes. When a subroutine is first called, the return address is pushed onto the top of the stack. After the subroutine completes, the return address is popped from the stack. The stack is 2 levels deep by default and can be lengthened to 8 levels by setting the Stack Extend or STACKX option. Since the stack is relatively shallow even when extended, stack overflows will occur if you aren't careful with subroutine calls and recursion should definitely be avoided. Some instruction orders are not compatible with turbo mode and may cause faulty program execution so non-turbo mode is also known as computability mode.

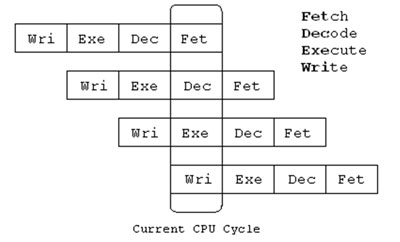

Four-stage Instruction Pipeline

The pipeline consists of four stages:

- Fetch – The instruction is fetched from memory.

- Decode – The instruction is decoded.

- Execute – The instruction is executed

- Write – The result of the instruction is written to its destination.

The pipeline advances one stage each cycle and additional instructions are loaded each successive cycle. When the pipeline is full and turbo mode is enabled, one instruction completes every cycle. The pipeline must be flushed during jump instructions as well as other instructions that alter the program counter.